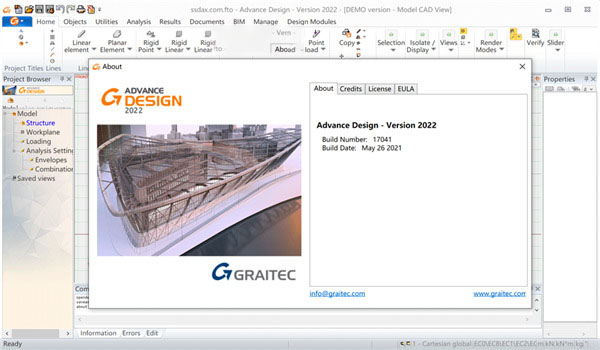

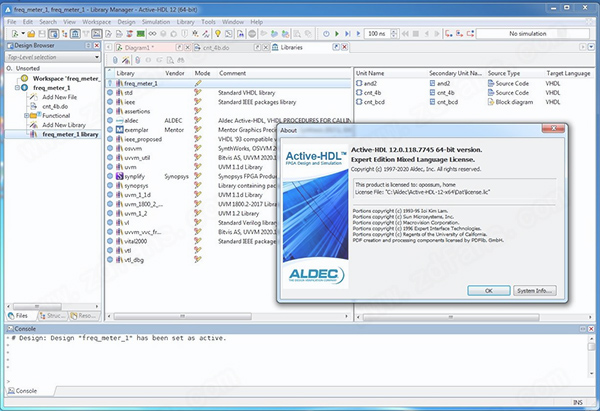

Aldec ActiveHDL12破解版下载|Aldec Active-HDL 12 中文版v12.0.118.7745下载

Aldec Active-HDL 12是一个专业的FPGA设计仿真平台,知识兔支持所有领先的C/HDL合成和实现工具,并且知识兔兼容业界标准,如IEEE、ISO、IEC及其它标准等它都支持。知识兔可以给用户带来全面的设计覆盖率。同时它还具备排错工具,能支援Soft或Hard IP Core元件。最新版本中增加了对开源VHDL验证方法、还增强了SystemVerilog和对未解析的用户定义的网络类型的初步支持。更多强大的功能用户可以自己下载体验。本次分享的是中文破解版,下方有着详细的安装破解教程。

软件功能

1、Aldec, Inc.是FPGA和ASIC设计的混合HDL语言仿真和硬件辅助验证的先驱,已增强以支持VHDL-2019 (IEEE 1076-2019)中的新特性。这些特性简化了语言,解除了早期版本中存在的某些限制,并引入了新的应用程序编程接口(api)。

2、还增强了SystemVerilog,知识兔包括对实例的多维数组的初步支持,对未解析的用户定义的网络类型的初步支持,知识兔以及对惟一约束的初步支持。

3、最新版本中也出现了一些对SystemVerilog的非标准扩展。这包括允许由连续赋值驱动可变类型的时钟块输出,允许使用foreach循环遍历子数组的元素,知识兔以及将带modport的虚拟接口赋值给不带modport的虚拟接口。

4、是为开发VHDL、Verilog/SystemVerilog、EDIF和SystemC设计而设计的集成环境。它包含的几个设计输入工具,高密度脂蛋白/ SystemC编译器单一仿真内核,几个标准和先进的调试工具,图形和文本仿真输出的观众,和许多辅助工具设计设计,便于管理、资源文件,和库以及内置的接口,允许运行模拟、合成、或实现本地或远程计算机,控制源文件的修订,或者与分享仿真模型的第三方工具通信。

5、分享了一组强大的向导,知识兔可以方便地创建新的工作空间、设计或设计资源,知识兔包括VHDL、Verilog、SystemC源文件、块或状态图、test长凳等。

6、从图形用户界面执行的大多数操作也可以通过软件宏语言的命令调用。通过编写自己的宏,知识兔可以显著改进测试和自动化设计处理。软件还为Perl和Tcl/Tk分享脚本引擎。通过创建用户定义的脚本,您可以通过添加额外的窗口、扩展宏语言以及分享外部工具和软件产品的接口来增强Active-HDL 12设计环境。

7、套件还包括VSimSA,一个为批处理设计的独立的VHDL/Verilog/SystemVerilog/EDIF/SystemC仿真环境。在功能上,VSimSA完全独立于软件。VSimSA与软件的区别在于缺少图形用户界面(GUI)。VSimSA命令和程序完全由命令行发出和控制,这在自动化设计测试中特别有用。

安装方法

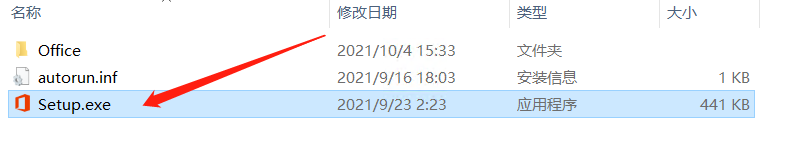

1.在知识兔下载好数据包后进行解压得到安装程序“Active-HDL_12.0.118.7745_x64_main_setup.exe”,鼠标知识兔双击运行进入安装向导知识兔点击“next”进入下一步

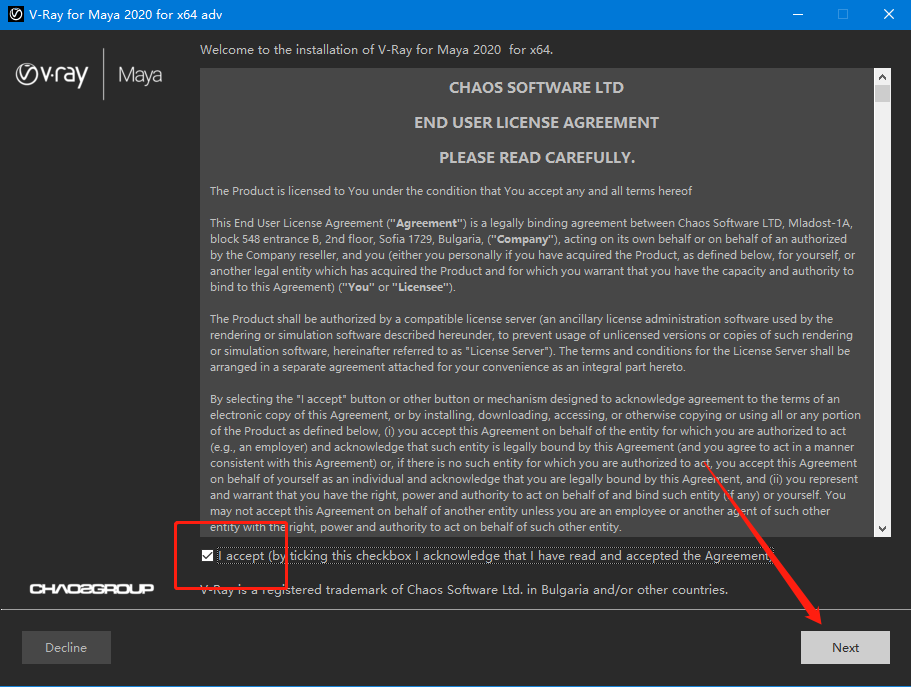

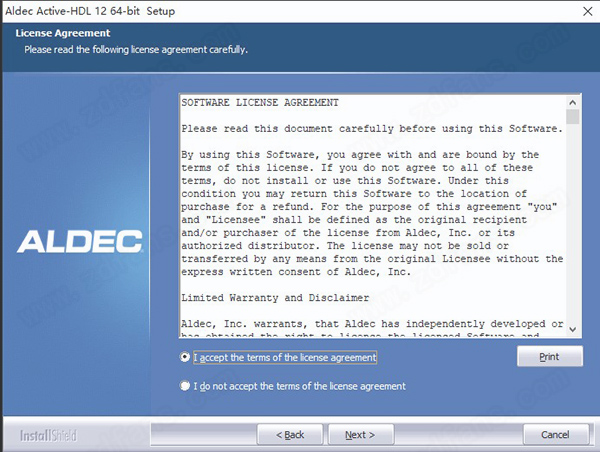

2.选择第一项“I accept the terms of the license agreement”(我接受许可协议的条款),再知识兔点击“next”进入下一步

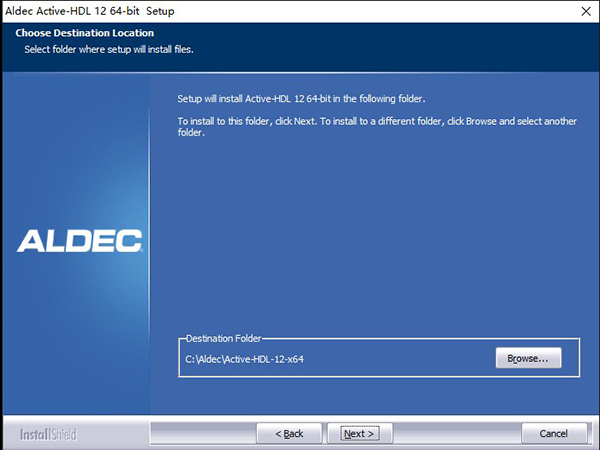

3.选择安装位置,默认路径为“C:\Aldec\Active-HDL-12-x64”,知识兔建议最好不要安装到系统盘(C盘)

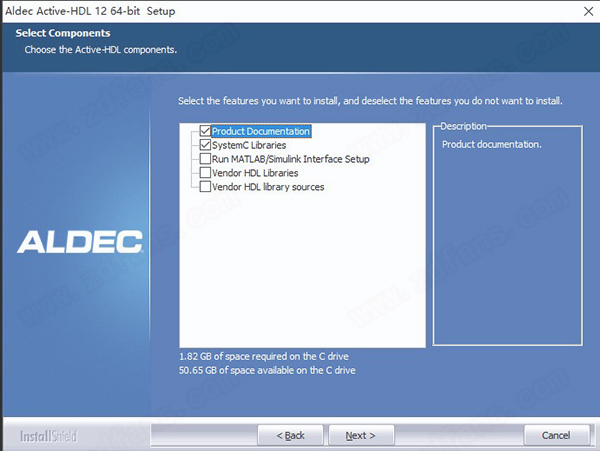

4.根据自身需求选择安装功能组件,需要安装的前面勾上即可

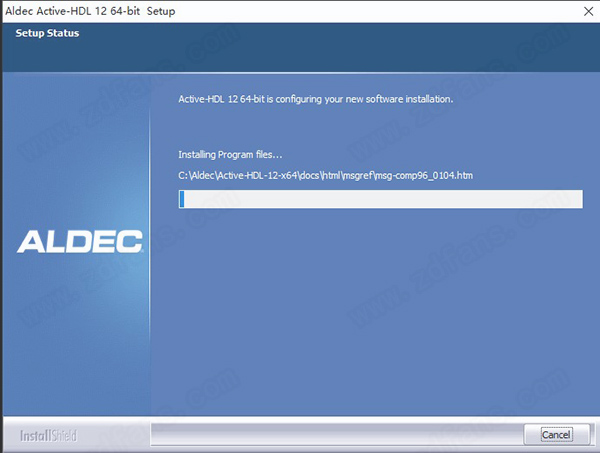

5.软件安装需要一些时间请耐心等待即可

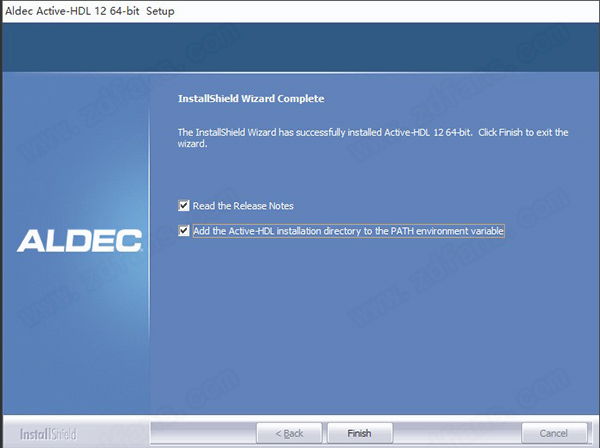

6.当安装完成后知识兔点击“finish”即可退出安装向导

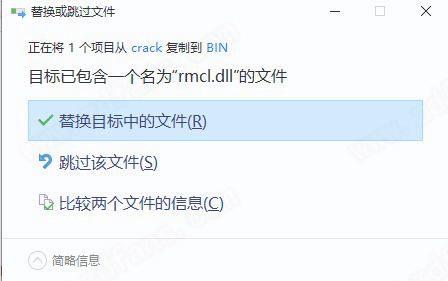

7.完成后先不要运行软件,回到刚才下载的数据包中将rmcl.dll复制到安装目录下的bin文件夹中,知识兔点击替换目标中的文件

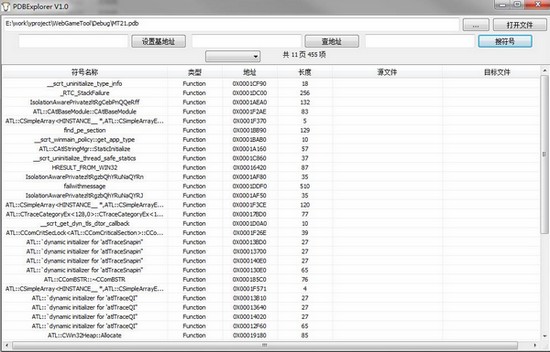

8.记事本方式打开license.dat,请确保将HOSTID = ANY_ID修改为您自己的名称,例如HOSTID =3C-7C-3F-ED-62-66

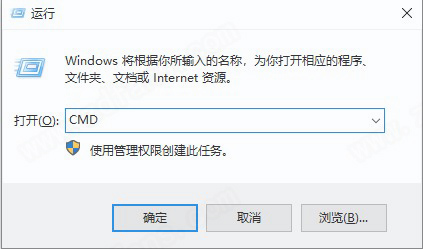

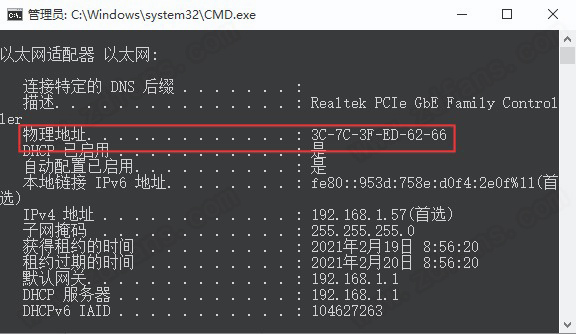

(1)我们首先需要知道电脑的HostID就是电脑的物理地址,按win+R键打开运行,知识兔输入cmd,

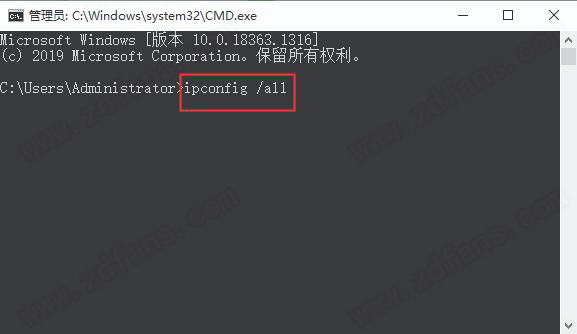

(2)第二步进去命令提示符之后,知识兔输入ipconfig /all,如下图所示:

(3)第三步按回车键之后,知识兔可以看到电脑的物理地址也就是电脑的HostID,如下图所示:

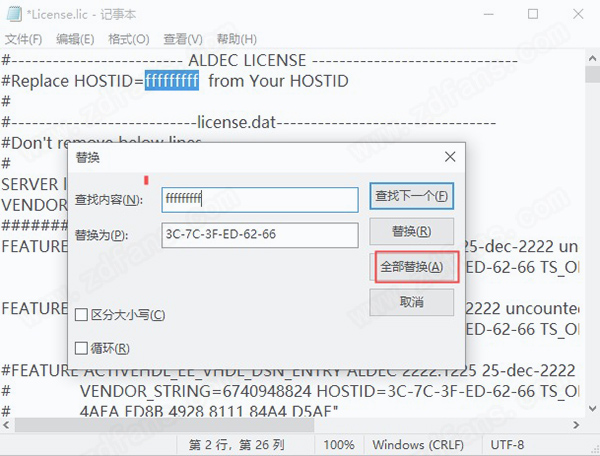

(4)小编的HostID为:3C-7C-3F-ED-62-66,这时以记事本的方式打开“License.lic”,知识兔点击“编辑”-“替换”,查找内容输入:原本的 HostID,替换内容输入“3C-7C-3F-ED-62-66”,最后知识兔点击全部替换即可,保存退出!

9.知识兔将“License.lic”复制到安装目录下DAT文件夹中

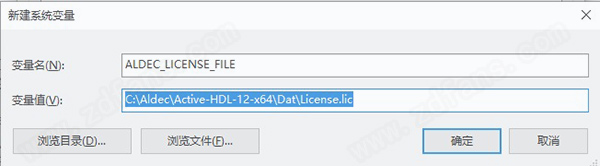

10.创建一个系统环境变量

变量名:ALDEC_LICENSE_FILE

变量值:license.dat的路径(例如C:\Aldec\Active-HDL-11.1-x64\Dat\ license.dat)

11.最后运行软件即可直接免费使用了

使用说明

1、一般

在使用VITAL模型的设计初始化期间,仅在加载SDF文件时启动负约束计算阶段。无论SDF文件的可用性如何,都应启动此阶段。

如果知识兔多次重新启动仿真,则可能会发生内部存储器碎片,导致内存分配增加。(DKO2370)

如果知识兔在模拟运行时关闭系统控制台窗口而中断VSimSA,则wave.asdb.error文件和wave.asdbw文件夹及其内容将保留在磁盘上。这些是临时项目,如果知识兔需要,用户可以安全地删除它们。此外,它们不会妨碍后续模拟会话,并在运行新模拟时自动删除。

无论如何,知识兔建议通过发出endsim命令来结束模拟。(MRP3553)

2、Verilog模拟

只有将所有文件编译到空设计库中时,顶级Verilog模块的自动检测才能正常工作。顶级检测不适用于单独编译的Verilog文件。

无法停止将信号记录到波形文件中。一旦在模拟过程中将信号添加到波形文件中(使用trace或addwave命令),它将具有完整的历史记录,直到模拟结束。

具有随机刺激器规范的$force任务不起作用(JKL59)。

3、SystemVerilog模拟

常规数组不能分配给动态数组,反之亦然。

不支持使用文字的作业。

类C操作符(+=,++,-等)不能操作队列/数组元素。

$sign不能用于引用队列的最后一个元素。(它只能在声明队列时使用。)

foreach循环不能用于迭代数组/队列元素。

系统功能,例如$size不适用于数组或队列。

通过将点和字段名称附加到索引名称(即数组/队列元素),无法访问类和结构的字段。

数据容器不能放在结构或类中。

动态数组,关联数组和队列的常规数组不可用。

几个对象类型(例如解压缩的结构或字符串)不能放在数组和队列中。

数据容器不能通过引用传递

下载仅供下载体验和测试学习,不得商用和正当使用。